随着无线通信技术的飞速发展,射频集成电路(RFIC)作为连接数字世界与无线信号的关键桥梁,其设计复杂性日益增加。从智能手机到物联网设备,从5G基站到卫星通信,RFIC的性能直接决定了整个系统的通信质量、功耗与成本。射频电路的工作频率高、信号微弱、对外界干扰敏感,设计过程充满了挑战。本文将深入解析射频集成电路设计中的常见核心问题,并提供相应的解决思路与方案。

一、 常见问题剖析

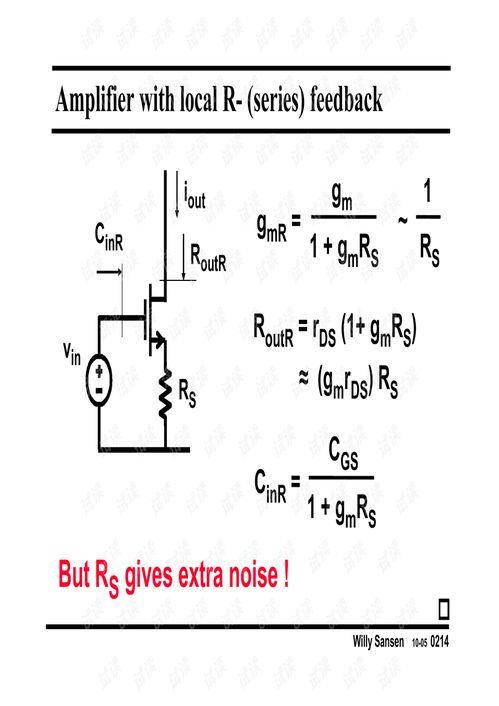

- 噪声与灵敏度问题

- 问题描述:射频接收机需要处理极其微弱的信号(可达微伏级)。放大器、混频器等有源器件内部产生的噪声,会淹没有用信号,导致接收灵敏度下降,通信距离缩短或误码率升高。

- 核心指标:噪声系数(NF)。

- 线性度与干扰问题

- 问题描述:在实际应用中,强干扰信号(阻塞信号)或自身产生的谐波、交调产物会落入接收信道,造成信号失真。这要求电路具有良好的线性度,以处理大信号而不产生严重失真。

- 核心指标:输入三阶交调点(IIP3)、1dB压缩点(P1dB)。

- 阻抗匹配与功率传输问题

- 问题描述:射频信号在传输过程中,若源端、传输线、负载端的阻抗不匹配,会导致信号反射,造成功率传输效率下降、增益波动,甚至引起电路不稳定(振荡)。

- 核心指标:反射系数(Γ)、电压驻波比(VSWR)、S参数(尤其是S11和S22)。

- 功耗与效率的平衡问题

- 问题描述:尤其在移动终端中,电池续航至关重要。功率放大器(PA)作为射频前端最耗电的模块,其效率直接决定整机功耗。但高效率(如开关类功放)和高线性度往往存在矛盾。

- 核心指标:功率附加效率(PAE)、整体系统功耗。

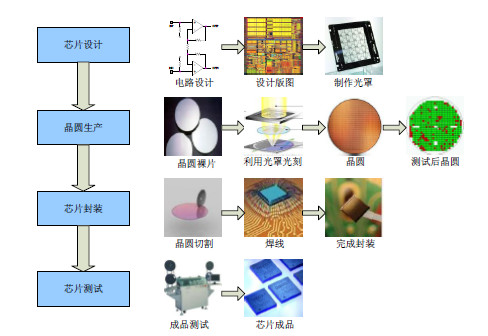

- 工艺变异与模型准确性

- 问题描述:深亚微米CMOS工艺是RFIC的主流,但晶体管在高频下的寄生效应(如衬底损耗、栅极电阻)显著,且工艺角(Process Corner)的波动会导致实际流片性能与仿真结果出现偏差。无源器件(电感、电容、传输线)的模型在高频下也更为复杂。

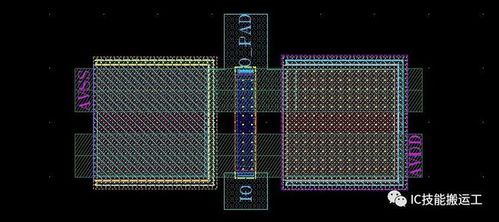

- 封装与测试的寄生效应

- 问题描述:封装引线的电感和焊盘的电容会引入额外的寄生参数,改变芯片内部的射频性能,可能导致频率响应偏移、增益下降或稳定性问题。测试探针和PCB板同样会引入误差。

二、 关键解决方案与设计策略

- 优化噪声性能

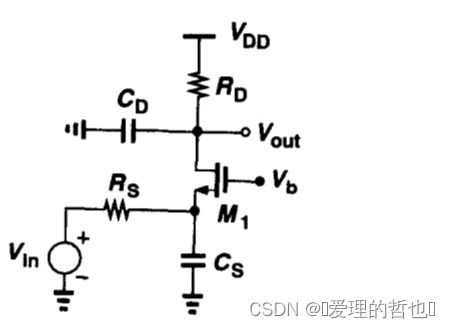

- 电路拓扑选择:在低噪声放大器(LNA)设计中,采用共源共栅(Cascode)结构以平衡增益与噪声;使用电感退化技术改善线性度和匹配。

- 器件尺寸与偏置优化:通过仿真精细调整晶体管宽度、偏置电流/电压,找到最小噪声系数(NFmin)的最佳工作点。

- 阻抗匹配网络设计:设计输入匹配网络,使源阻抗呈现为晶体管获得最小噪声所需的最佳噪声阻抗(Γopt),而非单纯追求功率匹配(S11最小)。

- 提升线性度

- 负反馈技术:采用源极负反馈(电感或电阻)来提升线性度,但会牺牲一定增益和噪声性能。

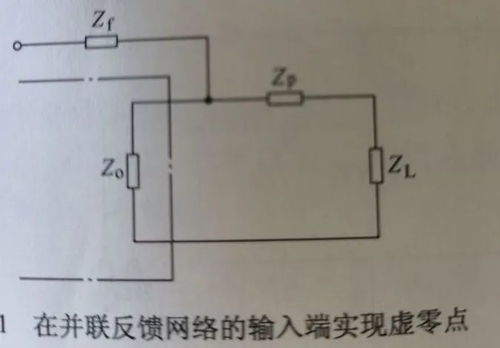

- 非线性补偿技术:如使用导数叠加(Derivative Superposition)等技术,利用辅助晶体管抵消主晶体管的非线性电流。

- 前馈/预失真技术:在功放等模块中,通过检测并注入反向失真信号来抵消非线性产物(更常用于板级或系统级)。

- 适当选择偏置点:工作在较高的偏置电流通常有利于线性度,但需与功耗权衡。

- 实现宽带阻抗匹配

- 使用LC匹配网络:通过π型、T型或L型网络进行窄带精确匹配。

- 宽带匹配技术:采用共源共栅结构、负反馈(电阻反馈)或变压器巴伦(Balun)来实现更宽频带的匹配,满足多频段/宽带系统需求。

- 片上ESD保护电路的特殊设计:避免ESD结构引入大的寄生电容破坏射频端口的匹配。

- 管理功耗与效率

- 架构创新:采用包络跟踪(ET)、平均功率跟踪(APT)等先进技术,使功放的供电电压随输入信号包络动态调整,大幅提升平均效率。

- 开关类功放设计:研究E类、F类等开关模式功放,理论上可实现100%的效率,但需解决线性化和宽带设计挑战。

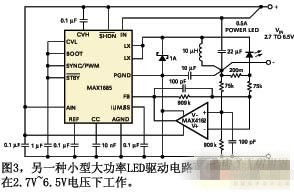

- 电源管理集成:在芯片内集成高效的直流-直流转换器(DC-DC),为功放提供可调电压。

- 应对工艺与模型挑战

- 设计留有余量(Margin):在仿真时充分考虑工艺角、电压、温度(PVT)变化,确保在最坏情况下电路仍能满足指标。

- 采用稳健设计:优先选择对工艺变化不敏感的电路结构和器件尺寸。

- 可测试性设计(DFT)与微调(Trimming):在芯片中集成关键性能(如频率、增益)的检测电路和可调元件(如电容阵列),以便在测试或使用时进行校准。

- 抑制寄生与协同设计

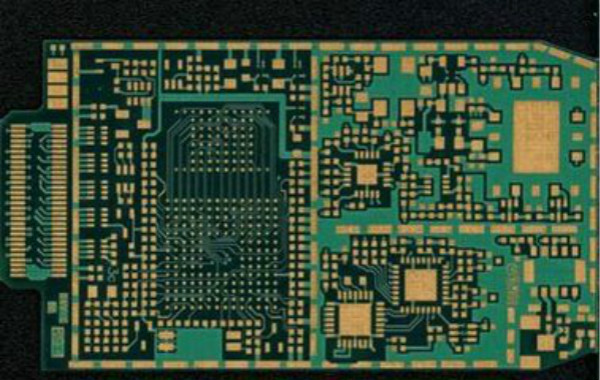

- 芯片-封装协同设计(CPC):在设计的早期阶段就将封装模型(包含键合线、焊球、封装基板)纳入整体仿真,优化I/O布局和匹配网络。

- 使用先进封装:采用倒装芯片(Flip-Chip)、扇出型(Fan-Out)等封装技术,缩短互连长度,减少寄生电感。

- 片上隔离技术:使用深N阱、保护环、隔离槽等技术,减少衬底噪声耦合和干扰。

****

射频集成电路设计是一门需要深厚理论功底、丰富工程经验和不断创新的艺术。面对噪声、线性度、匹配、功耗等相互制约的挑战,设计师必须在复杂的多维参数空间中寻找最优解。随着工艺节点不断演进和系统需求日益苛刻,未来的RFIC设计将更加依赖于先进的设计方法学、精准的工艺模型以及芯片-封装-系统级的协同优化。只有深入理解问题的物理本质,并灵活运用各种电路技术和设计策略,才能设计出高性能、高可靠性的射频集成电路,持续推动无线通信技术的边界。