在模拟集成电路的设计与制造中,确保芯片的可靠性、功能完整性与长期稳定性是核心目标。其中,静电放电(ESD)保护电路与焊盘(PAD)电路的设计,是连接芯片内部精密模拟世界与外部物理封装环境的关键桥梁,它们直接关系到芯片能否在实际应用中抵御外部电气冲击并实现可靠的电学连接。本文将遵循典型的模拟集成电路设计流程,阐述ESD保护电路与PAD电路的设计要点及其在流程中的位置与作用。

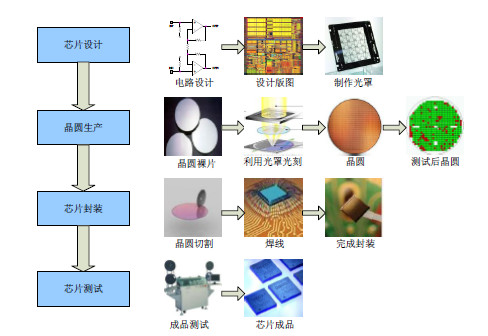

一、模拟集成电路设计流程概览

典型的模拟集成电路设计流程是一个迭代、求精的过程,主要包含以下几个阶段:

- 系统定义与指标制定:明确芯片的功能、性能指标(如增益、带宽、噪声、功耗等)、工作条件及封装形式。

- 架构设计与电路设计:根据指标,选择或设计合适的电路架构(如运算放大器、比较器、数据转换器等),并使用晶体管级电路进行实现,进行初步的仿真验证。

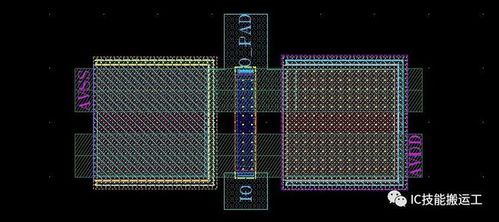

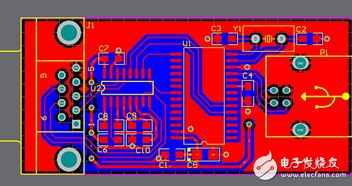

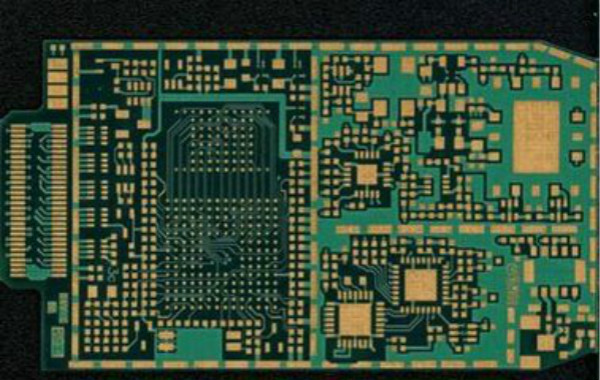

- 版图设计与物理实现:将电路原理图转化为实际的几何图形(版图),这是连接电路设计与芯片制造的物理桥梁。此阶段必须严格遵守设计规则(DRC),并考虑寄生效应。

- 后仿真与验证:提取版图的寄生参数(电阻、电容),反馈到电路仿真中,验证物理实现后的电路性能是否依然满足指标。同时进行电气规则检查(ERC)、版图与原理图一致性检查(LVS)。

- 可靠性设计与验证:这是ESD保护电路与PAD电路设计的核心环节。需要专门进行ESD鲁棒性设计、闩锁效应(Latch-up)防护设计,并进行相应的仿真与规则检查。

- 流片与测试:将最终确认的版图数据(GDSII文件)交付给晶圆厂制造,芯片返回后进行封装和全面的性能与可靠性测试。

ESD保护电路和PAD电路的设计,主要深度融入在 “版图设计” 与 “可靠性设计与验证” 阶段。

二、PAD电路:芯片与外部世界的接口

焊盘(PAD)是芯片上用于连接封装引线或探针的金属区域,是信号、电源和地进出芯片的物理端口。PAD电路的设计围绕PAD展开,其主要功能包括:

- 机械连接:提供足够大的金属面积,以利于引线键合或倒装芯片连接,保证连接的牢固性。

- 电学连接:作为低电阻通路,将外部信号或电源引入内部电路。

- ESD防护的锚点:PAD通常是ESD事件(如人体放电模型HBM、机器模型MM)的首要冲击点,因此它是集成ESD保护结构的核心位置。

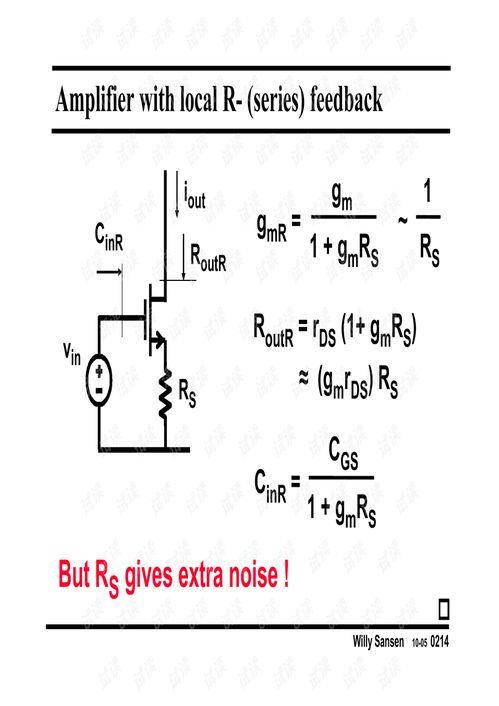

- 输入/输出缓冲:对于I/O PAD,内部通常包含输入缓冲器(将外部信号转换为内部逻辑电平)或输出驱动级(将内部信号驱动到外部负载)。在模拟电路中,输入PAD可能直接连接高阻抗节点,需特别考虑泄漏和噪声。

PAD电路的设计需在版图阶段精心规划,确保金属线宽、间距满足电流密度要求,并考虑信号完整性(如串扰)。

三、ESD保护电路:芯片的“防雷击”系统

静电放电(ESD)是集成电路在制造、封装、测试及使用过程中面临的主要可靠性威胁之一。ESD保护电路的作用是在ESD事件发生时,在极短时间内(纳秒级)为瞬态大电流提供一条安全的、低阻抗的泄放通路,将PAD上的电压钳位在安全范围内,从而保护内部脆弱的栅氧层和晶体管。

核心设计要点包括:

1. 保护拓扑结构:常见的ESD保护单元包括:

* 基于二极管的结构:利用二极管的正向导通和反向击穿特性泄放电流。结构简单,寄生电容小,适合高速I/O,但钳位电压相对固定。

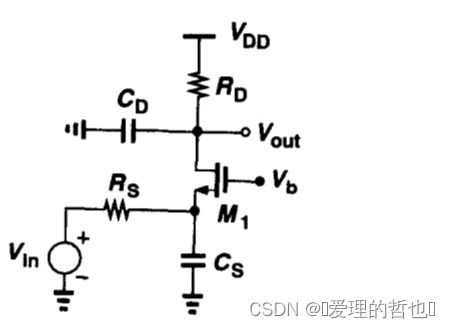

- 栅极接地的NMOS(GGNMOS):最常用的结构之一。在ESD事件下,其寄生双极型晶体管(NPN)被触发导通,形成低阻通路。其触发电压和维持电压是关键设计参数。

- 可控硅整流器(SCR):单位面积泄放电流能力最强,但触发电压可能较高,且存在闩锁风险,需谨慎使用。

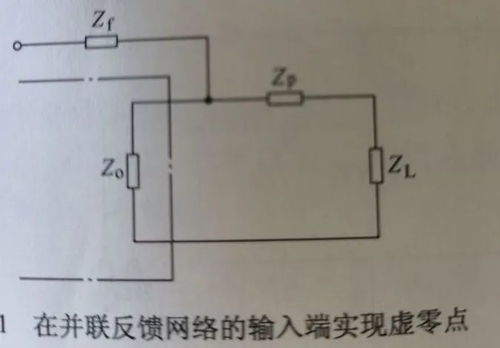

- 两级保护策略:为了兼顾响应速度与泄放能力,常采用两级保护。

- 第一级(主保护):位于PAD附近,通常采用大尺寸器件,用于泄放绝大部分ESD电流,承受主要能量冲击。

- 第二级(次级保护):位于内部电路输入端附近,尺寸较小,用于钳制第一级保护后可能残留的过冲电压,提供精细保护。两级之间通常用串联电阻隔离。

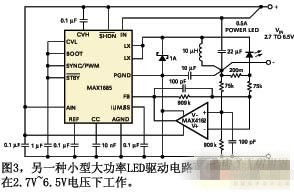

- 全芯片ESD保护网络:不仅要保护每个I/O PAD,还需设计电源轨(VDD到VSS)之间的保护电路(如电源钳位电路),确保任何组合引脚之间(如I/O到VDD, I/O到VSS, VDD到VSS)都有有效的ESD泄放路径。

- 版图实现:ESD器件的版图设计有特殊规则,例如采用“叉指”结构增加周长、添加足够的接触孔、确保电流均匀分布、遵守安全的间距规则以防止二次击穿等。

四、设计流程中的协同与验证

在完整的模拟IC设计流程中,ESD/PAD设计并非孤立环节:

- 在电路设计阶段,就需要预估PAD和ESD结构引入的寄生电容(尤其是对高速、高频模拟信号的影响),并将其纳入整体性能仿真。

- 在版图设计阶段,必须根据晶圆厂提供的ESD设计规则(ESD Rule Deck)进行布局布线。PAD的位置规划、ESD保护环(Guard Ring)的绘制、电源/地网络的布局都至关重要。

- 在验证阶段,除了常规的DRC/LVS,必须执行专门的ESD规则检查(ESD Check),确保所有保护结构符合规范,泄放路径完整且低阻。还可能进行传输线脉冲(TLP)特性的电路级仿真,以预测ESD器件的触发特性。

结论

ESD保护电路与PAD电路是模拟集成电路从设计图纸走向可靠产品的关键保障。它们的设计紧密集成于芯片的物理实现与可靠性验证流程之中。优秀的ESD/PAD设计需要在保护能力、信号完整性、面积开销和工艺兼容性之间取得精妙平衡。随着工艺节点不断演进,内部晶体管栅氧层日益脆弱,而封装形式愈发多样,这对ESD保护与接口电路的设计提出了更高要求,使其成为模拟及混合信号IC设计中不可或缺的专业领域。