运算放大器(Op-Amp)和比较器(Comparator)是两种在模拟集成电路设计中极为常见且功能强大的器件。它们在电路符号上相似,内部结构也有重叠之处,例如都包含高增益的差分输入级。它们的核心设计目标、工作原理、性能指标和应用场景存在根本性的区别,理解这些差异对于正确选择和设计电路至关重要。

1. 核心功能与设计目标

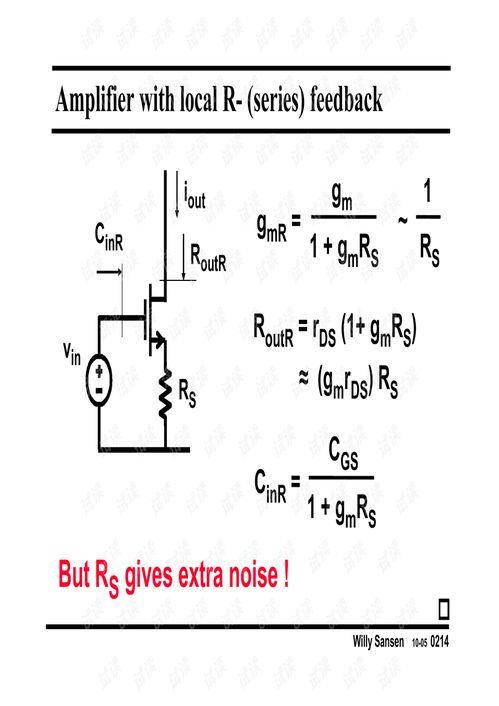

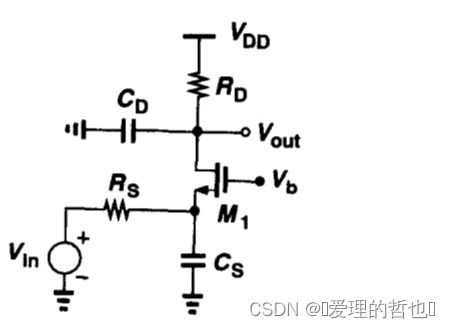

- 运算放大器:其设计目标是实现一个高增益、高线性度的电压放大器。在负反馈配置下(如反相、同相放大器),其输出与输入之间呈现精确、稳定的线性关系。运算放大器的“理想”状态是虚短(输入电压差趋于零)和虚断(输入电流趋于零),其开环增益越高,闭环线性度越好。

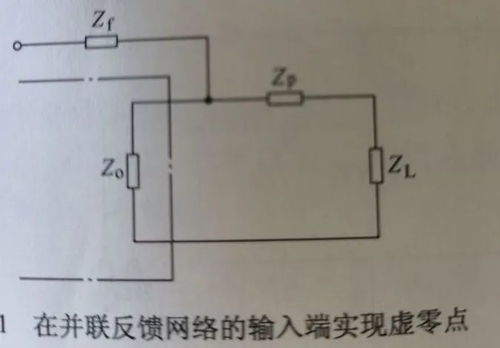

- 比较器:其设计目标是快速、准确地比较两个模拟电压的大小,并输出一个明确的高低电平(数字逻辑信号)。它工作在开环或正反馈(迟滞比较器)状态,其输出在输入电压差跨越阈值时发生“翻转”,旨在实现模拟到数字的转换。

2. 内部结构的关键设计差异

- 输出级:这是两者最显著的结构差异。

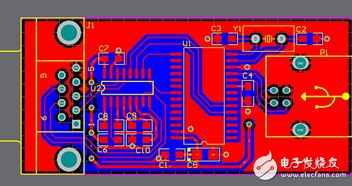

- 运算放大器:通常采用推挽输出级,能够双向(源电流和吸电流)驱动阻性负载,并设计为在负反馈下稳定工作,避免输出饱和。其压摆率(Slew Rate)和带宽需平衡,以确保线性放大时的信号保真度。

- 比较器:输出级通常是开漏(Open-Drain)或推挽数字输出,旨在快速驱动数字逻辑门(如CMOS、TTL电平)。为了追求极快的翻转速度,比较器通常不内置频率补偿电容,这使其在负反馈下极易振荡。其压摆率是核心指标,要求尽可能高。

- 响应速度与稳定性:

- 运算放大器:通过内部频率补偿(如米勒补偿)来确保在任何闭环增益下的稳定性,但这牺牲了带宽和压摆率。其建立时间(Settling Time)是关键指标。

- 比较器:不进行内部频率补偿,从而获得极高的响应速度。其关键指标是传播延迟(Propagation Delay),即从输入过阈值到输出完成翻转的时间。

- 输入失调电压:两者都追求低失调,但对比较器而言,失调电压直接影响比较精度和阈值准确性,在高速比较器中需特别优化。

3. 性能指标侧重点

- 运算放大器重点指标:开环增益、增益带宽积(GBW)、压摆率、建立时间、输入失调电压与漂移、共模抑制比(CMRR)、电源抑制比(PSRR)、噪声等。

- 比较器重点指标:传播延迟、压摆率、输入失调电压、迟滞(可内置或外设)、输出电平兼容性、最小过驱动电压下的响应时间等。

4. 应用场景与使用禁忌

- 运算放大器典型应用:模拟信号放大、滤波(有源滤波器)、数学运算(加、减、积分、微分)、精密电压基准、模拟伺服控制等线性电路。

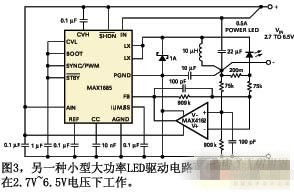

- 比较器典型应用:模数转换(ADC)的前端、电压监测与门限检测、方波/脉冲波生成、波形整形、数字接口电平等非线性开关电路。

- 重要禁忌:

- 切勿将比较器当作运放用于闭环线性放大。由于其无内部补偿,接入负反馈会产生严重振荡。

- 通常不建议将运放当作比较器使用。当运放开环工作时,其输出饱和到电源轨的速度较慢(压摆率低),且饱和恢复时间长。其输出电平可能不符合数字逻辑要求,传播延迟也远大于专用比较器。仅在速度、精度要求极低的场合可勉强替代。

5. 集成电路设计考量

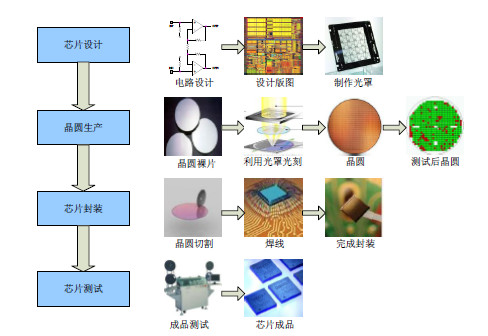

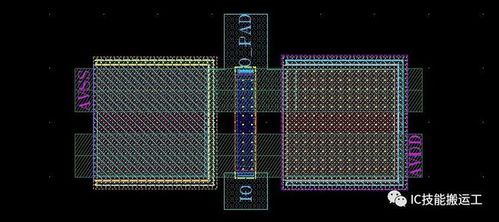

在芯片设计层面,设计师会根据上述不同目标进行优化:

- 对于精密运放,会采用复杂的电路结构(如自动归零、斩波稳定)来抑制失调和漂移,精心设计补偿网络以保证稳定性。

- 对于高速比较器,会采用锁存(Latch)结构、预放大器链来最小化传播延迟,并优化输出级以实现与数字电路的无缝连接。

###

简而言之,运算放大器是为“放大”而生,追求线性与稳定;比较器是为“判决”而生,追求速度与明确。在集成电路设计中,选择正确的器件并理解其底层设计哲学,是确保系统性能、可靠性和成本优化的关键一步。混淆二者的使用,往往是电路失效或性能不佳的常见根源。