集成电路设计是现代电子工业的基石,它将抽象的电路构想转化为能在硅片上精确制造的物理实体。整个过程可以比作建造一座宏伟的摩天大楼,其中‘集成电路设计’是涵盖从建筑设计到结构工程的完整蓝图规划,而‘集成电路布图设计’则是将蓝图转化为每一块砖、每一根钢筋精确位置和连接的施工图纸。两者紧密相连,共同构成了芯片诞生的核心路径。

一、集成电路设计:从构想到逻辑

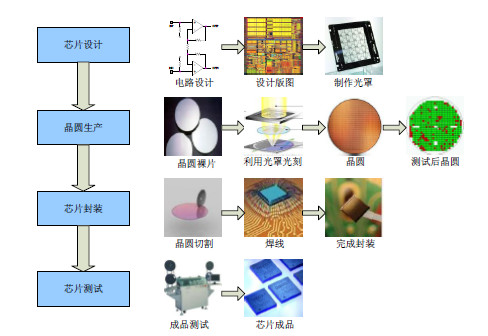

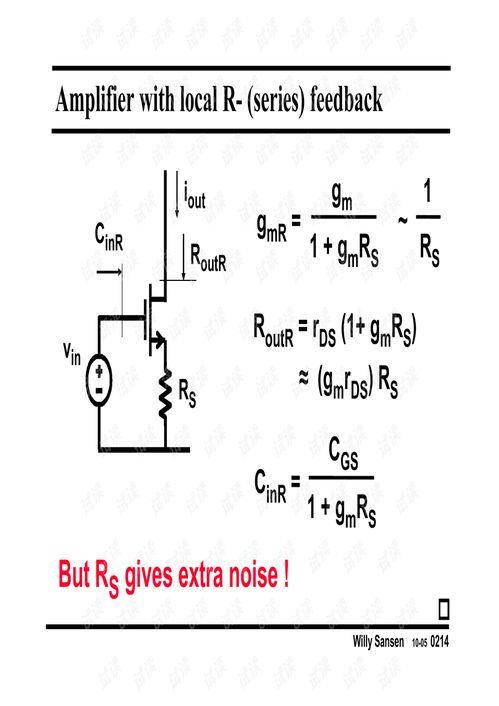

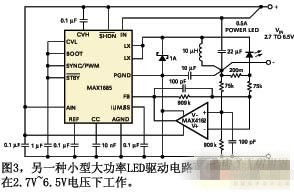

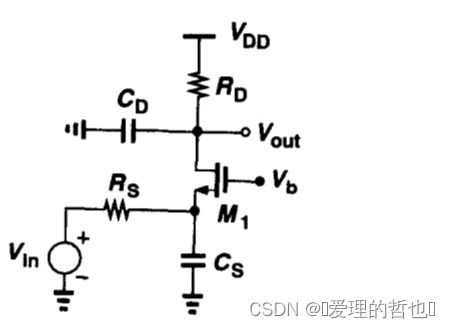

集成电路设计是整个芯片开发流程的上游环节,其核心目标是将系统功能或算法需求,转化为可供后续物理实现的技术方案。这一过程通常从系统级设计开始,通过硬件描述语言(如Verilog或VHDL)定义芯片的功能和行为,建立‘寄存器传输级’模型。通过逻辑综合工具,将这一高级描述转换为由标准逻辑单元(如与门、或门、触发器)组成的门级网表。此时的电路仍是逻辑和功能层面的抽象描述,确定了‘做什么’,但尚未定义‘如何做’——即晶体管、连线等物理元素在硅片上的具体形态、位置和连接关系。

二、集成电路布图设计:从逻辑到物理

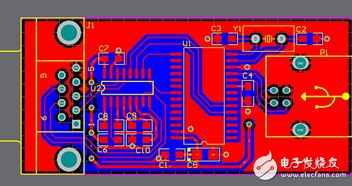

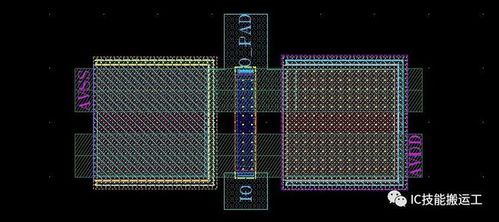

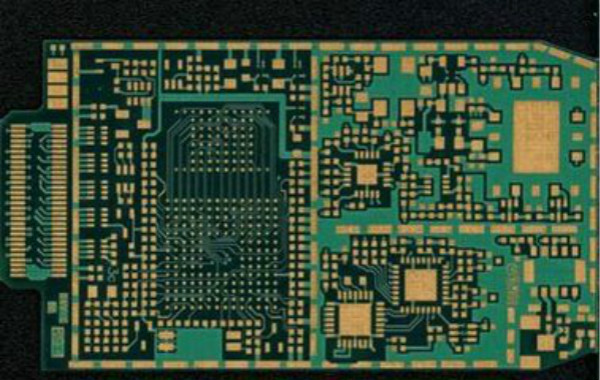

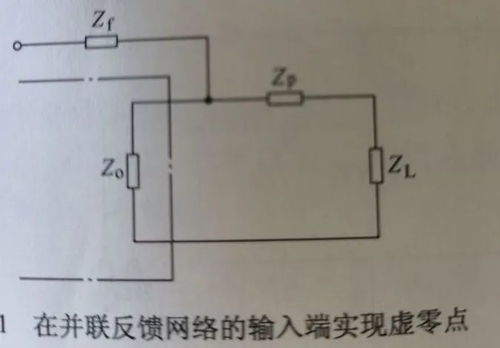

布图设计,又称为物理设计,是衔接逻辑设计与芯片制造的桥梁,是设计流程中技术最密集、挑战最大的阶段之一。其任务是将门级网表转化为可供光刻掩模版使用的几何图形数据,即版图。这个过程犹如为一座复杂的城市绘制详细的市政地图,需要精确规划每一个“建筑”(晶体管、逻辑单元)的位置、形状,以及连接它们的“道路”(互连线)的走向和宽度。

布图设计主要包含以下几个关键步骤:

- 布局:确定芯片上各个功能模块以及模块内所有标准单元或定制单元的物理位置。布局的目标是在满足时序、功耗和面积约束的前提下,优化单元摆放,为后续布线创造有利条件,并尽量减少芯片总面积。

- 布线:根据电路的连接关系,在已经固定的单元之间,按照工艺设计规则,规划并生成金属互连线。布线需要处理数百万甚至数十亿个连接点,确保所有信号正确连通,同时优化线长以减少延迟和串扰,并满足电流承载能力等电学要求。

- 时序收敛与优化:在布局布线过程中及之后,需要反复进行静态时序分析,确保信号能在时钟约束下正确传输。通过调整单元尺寸、插入缓冲器、优化时钟树等方式,解决建立时间和保持时间的违规问题,是布图设计的核心挑战。

- 物理验证:完成初步版图后,必须进行严格的验证,包括设计规则检查(确保版图符合晶圆厂的制造工艺极限)、电气规则检查(检查电学连接的合理性)以及版图与原理图一致性检查(确保物理连接与原始逻辑设计完全一致)。

三、设计与布图:相辅相成的迭代过程

在实际项目中,集成电路设计与布图设计并非严格的线性流程,而是一个高度迭代、反复优化的循环。逻辑设计的决策(如架构选择、模块划分)会深刻影响布图的难度和结果(如布线拥塞、时序性能)。反之,布图阶段反馈的物理信息(如实际线延迟、功耗热点)也可能迫使设计阶段进行修改或优化。随着工艺节点进入纳米尺度,这种前后端的协同设计变得至关重要。先进的设计方法学,如物理综合,更是将布局、时序优化等物理信息提前引入逻辑综合阶段,以实现更好的整体质量。

四、面临的挑战与未来趋势

随着摩尔定律的持续推进,集成电路布图设计面临着前所未有的挑战:工艺尺寸微缩带来的量子效应、日益严峻的功耗墙、信号完整性问题、以及设计复杂度的指数级增长。为了应对这些挑战,自动化电子设计工具的作用愈发关键,人工智能与机器学习技术正被广泛应用于布局预测、布线优化和时序分析中,以提升设计效率和质量。基于芯粒的先进封装技术,也使得布图设计从单一的二维平面向2.5D/3D堆叠的立体空间拓展,开辟了新的设计维度和优化可能。

###

总而言之,集成电路设计是赋予芯片‘灵魂’的创意与规划过程,而集成电路布图设计则是塑造其‘躯体’的精密与严谨的艺术。二者一脉相承,共同将人类智慧的抽象结晶,转化为驱动数字世界的微观引擎。在信息时代,掌握并不断革新这两项核心技术,是推动半导体产业持续前进的根本动力。