CMOS(互补金属氧化物半导体)集成电路设计是现代电子工业的基石,从智能手机到数据中心,无处不在。它以其低功耗、高集成度和良好的抗噪能力,主导了当今的半导体产业。本文将系统性地介绍CMOS集成电路设计的关键概念、核心流程与发展趋势。

一、CMOS技术基础:互补之美

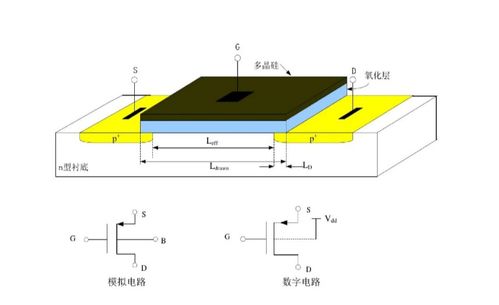

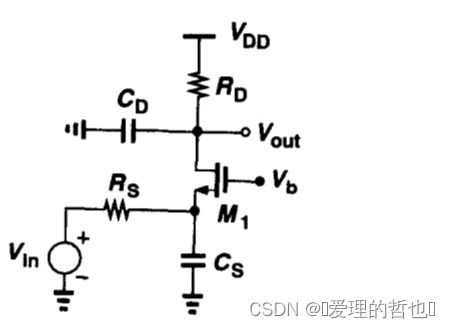

CMOS技术的核心在于巧妙地利用两种类型的MOSFET(金属氧化物半导体场效应晶体管):NMOS和PMOS。这两种晶体管以互补的方式工作。当输入为高电平时,NMOS导通而PMOS截止;当输入为低电平时,PMOS导通而NMOS截止。这种结构使得在稳态逻辑状态下(非切换瞬间),从电源到地之间不存在直接导通路,静态功耗理论上为零,这是CMOS低功耗优势的根本来源。

二、CMOS集成电路设计的主要流程

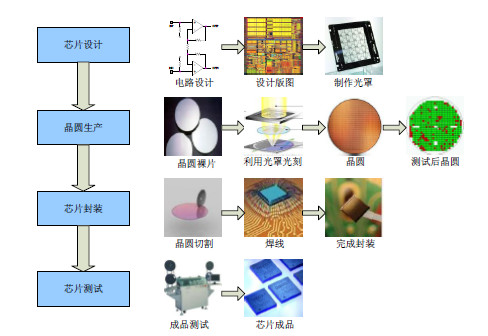

CMOS设计是一个高度复杂且迭代的过程,通常分为以下几个层次:

- 系统架构与规格定义:确定芯片的功能、性能指标(如速度、功耗、面积)、接口以及目标工艺节点。

- 逻辑设计与RTL编码:使用硬件描述语言(如Verilog或VHDL)将系统功能转化为寄存器传输级(RTL)描述。这是设计创造性的核心阶段。

- 逻辑综合:利用综合工具,将RTL代码、标准单元库和设计约束(时序、面积、功耗)作为输入,生成门级网表。

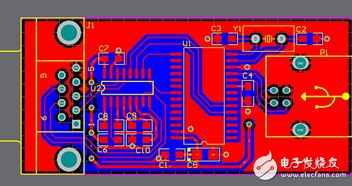

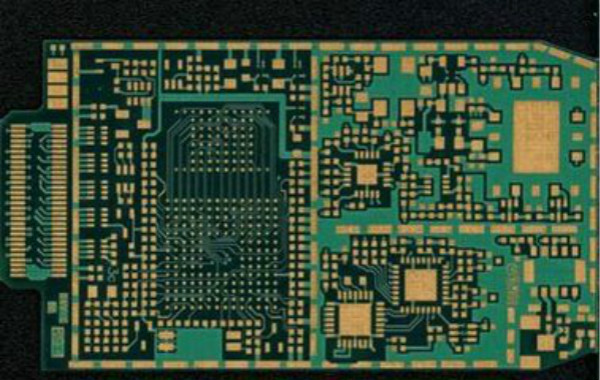

- 物理设计:这是将逻辑网表转化为实际几何版图的过程,包括:

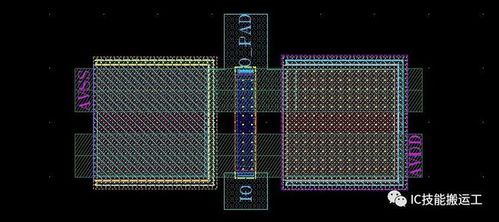

- 布图规划:确定芯片核心、存储器、I/O等模块的大致位置。

- 布局:将标准单元和宏模块放置在芯片上。

- 时钟树综合:构建低偏斜、低功耗的全局时钟分布网络。

- 布线:根据电气连接关系,在多层金属中完成单元间的互连。

- 验证与签核:在设计的每个阶段都需要进行严格验证,包括功能验证、时序验证(静态时序分析)、功耗分析、物理验证(设计规则检查、版图与原理图一致性检查)和信号完整性分析等,确保设计在投片前万无一失。

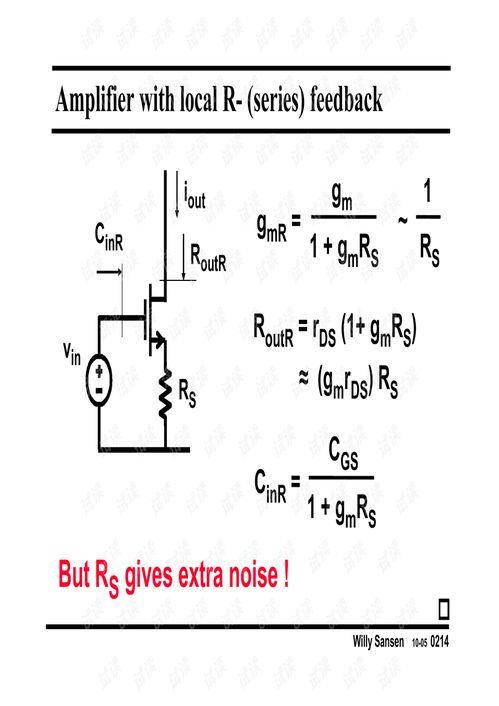

三、核心挑战与设计考量

随着工艺节点不断微缩至纳米尺度(如5nm、3nm),CMOS设计面临前所未有的挑战:

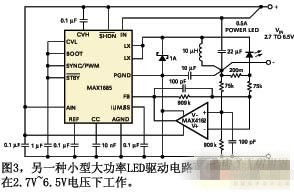

- 功耗管理:动态功耗和泄漏功耗的激增成为首要问题。设计师必须采用多电压域、电源门控、动态电压频率缩放等高级低功耗技术。

- 时序收敛:互连延迟的影响日益显著,信号完整性问题(如串扰)加剧,使得满足时序要求变得极其困难。

- 工艺变异:在极小尺寸下,晶体管特性的微观波动会导致性能与功耗的显著偏差,设计必须考虑工艺角、蒙特卡洛分析等以确保良率。

- 设计复杂性:数十亿晶体管的集成度要求强大的电子设计自动化工具和可重用IP(知识产权核)生态系统的支持。

四、未来发展趋势

CMOS技术仍在持续演进,并通过与其他技术结合开辟新路径:

- More Moore(延续摩尔定律):通过FinFET、GAA环绕栅极晶体管等新结构,继续微缩工艺节点。

- More than Moore(超越摩尔定律):通过系统级封装、芯粒技术,将不同工艺、功能的芯片(如模拟、射频、存储器)异构集成,提升系统性能。

- 新计算范式:针对人工智能等特定负载,设计专用的CMOS架构(如存内计算、近似计算),以突破能效瓶颈。

###

CMOS集成电路设计是一门融合了半导体物理、电路理论、计算机科学和系统工程的艺术与科学。尽管面临诸多挑战,但通过持续的技术创新和设计方法论进步,CMOS技术仍将在可预见的继续驱动整个信息社会的向前发展。对于设计者而言,掌握从系统架构到物理实现的完整知识链,并深刻理解工艺与设计之间的协同优化,是在这个领域取得成功的关键。